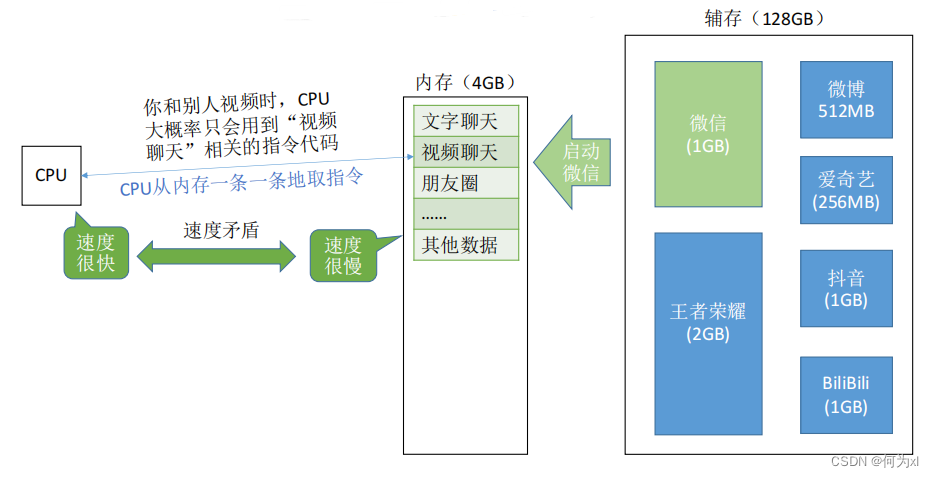

采用双端口RAM和多模块存储器提高存储器的工作速度,优化后速度与CPU差距依然很大。这时提出了 主存-Cache 的方式。

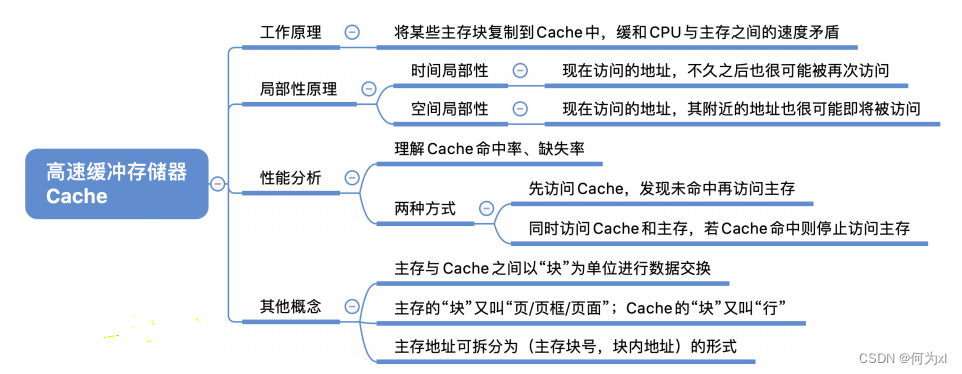

一、Cache的工作原理

基于局部性原理,把程序中正在使用的部分存放在一个高速的、容量教小的 Cache 中,使 CPU 的访存操作大多数针对 Cache 进行,从而大大提高程序的执行速度。

空间局部性:在最近的未来要用到的信息(指令和数据),很可能与现在正在使用的信息在存储空间上是邻近的。Eg:数组元素、顺序执行的指令代码。

时间局部性:在最近的未来要用到的信息,很可能是现在正在使用的信息。Eg:循环结构的指令代码。

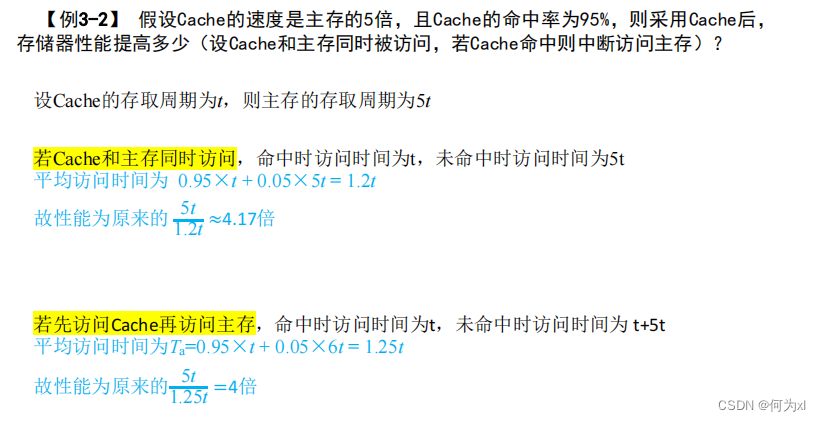

性能分析

设 t c t_ctc 为访问一次Cache 所需时间,t m t_mtm 为访问一次主存所需时间。

先访问Cache,若Cache未命中再访问主存:

t = H ∗ t c + ( 1 − H ) ∗ ( t c + t m ) t=H*t_c + (1-H)*(t_c + t_m)t=H∗tc+(1−H)∗(tc+tm)

同时访问 Cache 和主存,若 Cache 命中则立即停止访问主存:

t = H ∗ t c + ( 1 − H ) ∗ t m t=H*t_c + (1-H)* t_mt=H∗tc+(1−H)∗tm

二、使用 Cache 所必须解决的问题

如何区分 Cache 与 主存 的数据块对应关系? ——Cache和主存的映射方式。

Cache 很小,主存很大。如果Cache满了怎么办? ——替换算法。

CPU修改了Cache中的数据副本,如何确保主存中数据母本的一致性? ——Cache写策略。

关于 Cache和主存的映射方式、Cache替换算法、Cache写策略的详细内容,见下面链接文章:

链接:https://blog.csdn.net/weixin_43848614/article/details/126822309

作者:何为xl